## **SOLO - PAS HIS** PCBE differential charging evaluation

The material contained in this report is the property of CNES and may not be reproduced in any way, in whole or in part, without express authorization of the copyright holder in writing.

#### Denis PAYAN – CNES Pierre Sarrailh – Mohamed Belhaj – Virginie Inguimbert - ONERA

SOLO EMC WG- 8-9 Nov 2016

- Evaluation of a possible charge at a few volts of the ESD conductive painting PCBE (MAP<sup>™</sup>)

- The study

WP1 : Experimental Characterisation of the material property on 8 PCBE samples

WP 2 : SPIS Simulations

On WP1 SEE measurements at –51C and at room temperature, from10 eV to 5 keV.

Potential measurement at 100eV

Transversal resistivity measurement at -51C (if a potential is available on the surface)

On WP2, the WP measurements will be used in a SOLO S/C simulation

## WP1 Material conductivity

- PCBE Samples were too conductive to allow any measurement of the conductivity,

- A measurement in air with copper electrode is not a good method in that case,

- We can approximate the conductivity from current and voltage measurements  $J = \sigma E = \sigma V/d$

If we assume that V < 100 V :

σ = J . d / V σ > J . d / 100.0

σ > 3.10-9 Ω-1.m-1

Because of the uncertainty on this measurement a parametric study will be performed with

- Case 1 : infinite conductivity (ideal conductor)

- Case 2 : σ = 10-11 Ω-1.m-1

- Case 3 : σ = 10-13 Ω-1.m-1

- Case 4 : σ = 10-15 Ω-1.m-1

SOLO EMC WG- 8-9 Nov 2016

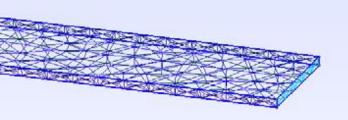

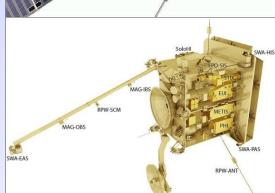

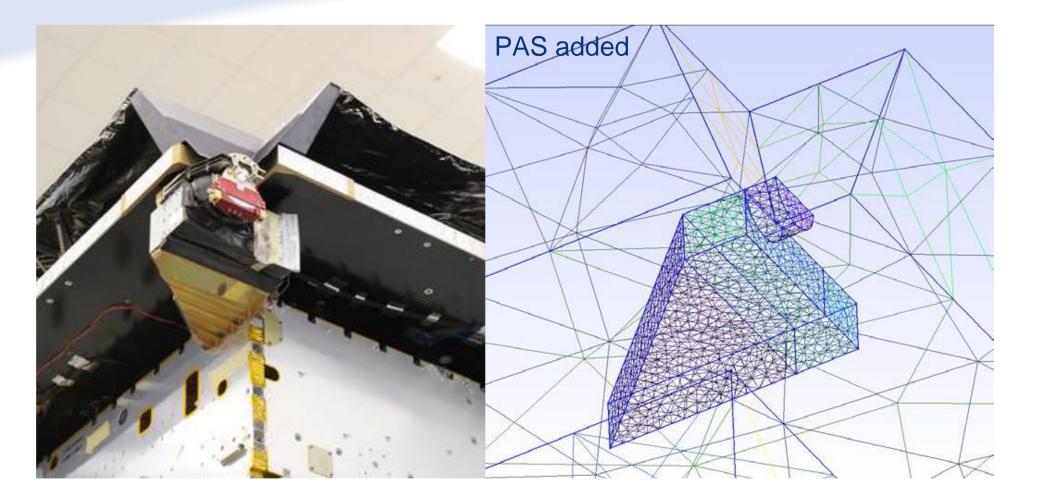

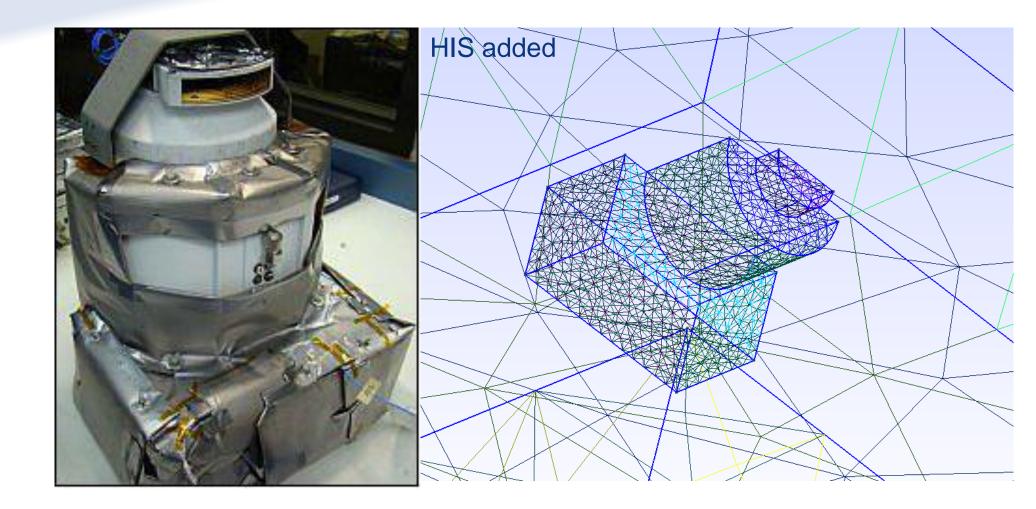

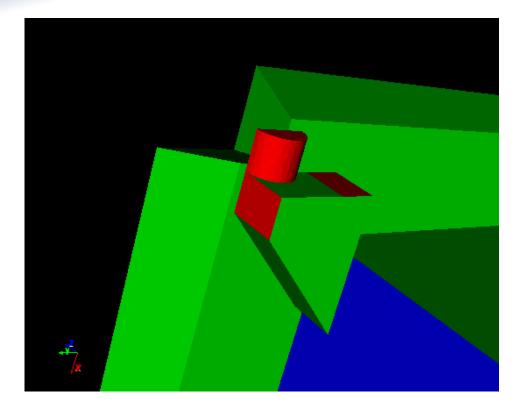

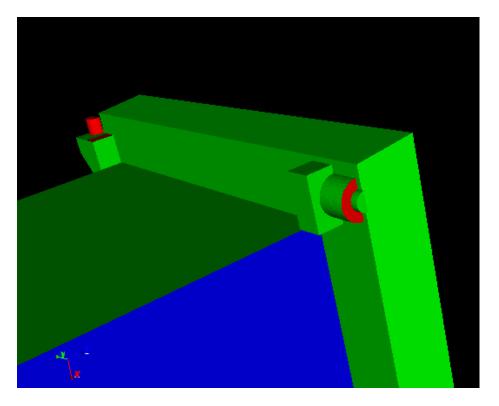

#### Cnes **SOLO GEOMETRY with PAS ans HIS**

## Same Cad than

### the one used by ESA

Simplified geometry for a better simulation efficiency **RPW** antennas and EAS detection head suppressed

Denis PAYAN (CNES)

SOLO EMC WG- 8-9 Nov 2016

SOLO EMC WG- 8-9 Nov 2016

SOLO EMC WG- 8-9 Nov 2016

# **C**COES Environmental test case

| Simulation ID              | 1 AU CASE                                 | 0.28 AU CASE                              |

|----------------------------|-------------------------------------------|-------------------------------------------|

| Distance (AU)              | 1                                         | 0,28                                      |

| Distance (Rs)              | 215                                       | 60,2                                      |

| Sun Flux (#1AU)            | 1,00                                      | 12,76                                     |

| Thermal elec. Model        | PIC - Maxwell<br>velocity<br>distribution | PIC - Maxwell<br>velocity<br>distribution |

| Ne_Core (m-3)              | 6,93E+06                                  | 1,04E+08                                  |

| Te_Core (eV)               | 8,14                                      | 21,37                                     |

| Ni (m-3)                   | 6,93E+06                                  | 1,04E+08                                  |

| Ti (eV)                    | 8,00                                      | 27,00                                     |

| Vz ram protons (km/s)      | 430,00                                    | 400,00                                    |

| Mach number                | 15,53                                     | 7,86                                      |

| Debye length (m)           | 8,06                                      | 3,38                                      |

| Debye length photoelec (m) | 0,98                                      | 0,27                                      |

## **C**COES Different material used

#### In RED the PCBE areas

SOLO EMC WG- 8-9 Nov 2016

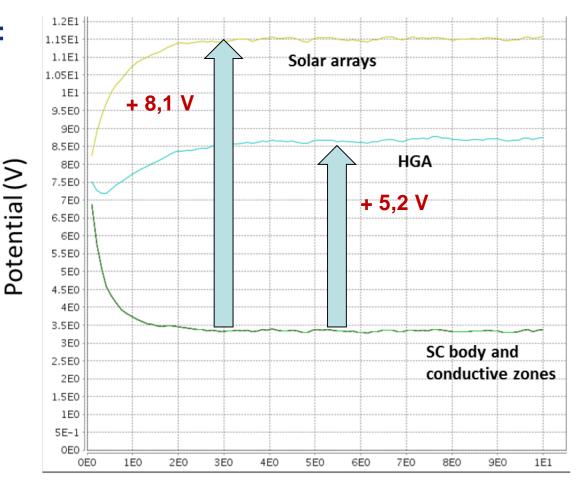

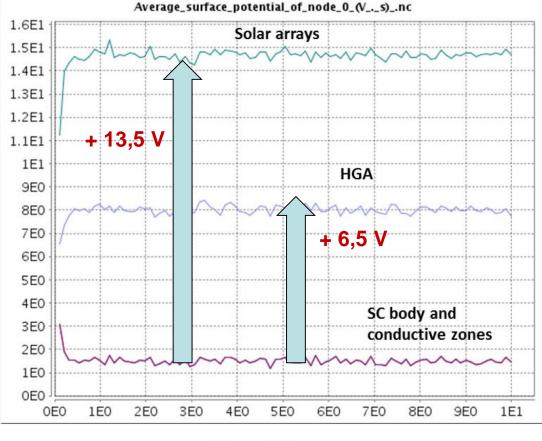

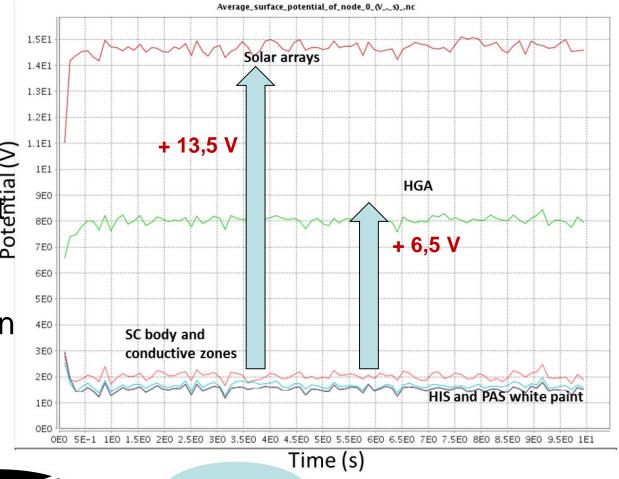

**CODES** Reference Test Case at 1UA/8eV : computed without painting (Or If Painting was totally conductive)

Conductive parts Potential: + 3.4 V

■ HGA Potential : +8.6 V

SUN Face Solar Array: +11.5 V

This simulation shows the voltage on all the S/C parts when there is no painting at 1UA

Time (s)

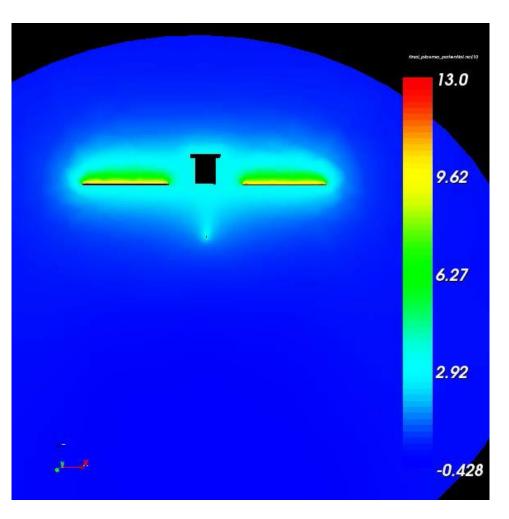

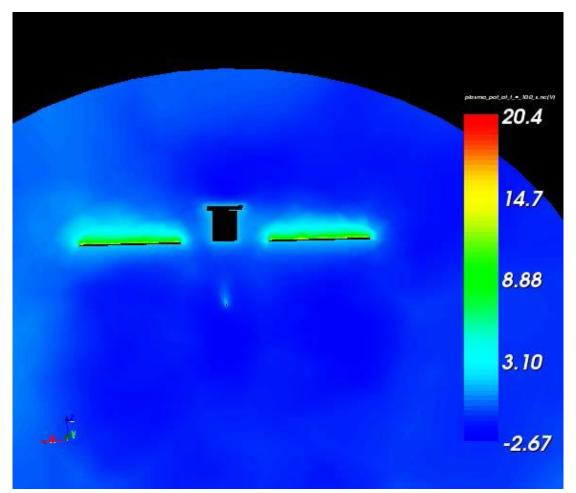

#### **COLS** Voltage Map at 1UA/8eV

This Volume voltage map shows that the voltage of instruments on the spacecraft surface is totally influenced by the S/C voltage which extend over some tens of centimeters in the surounding plasma (result compliant with a meter Debye length).

In good agreement with previous SOLO studies (RD 3 & 4)

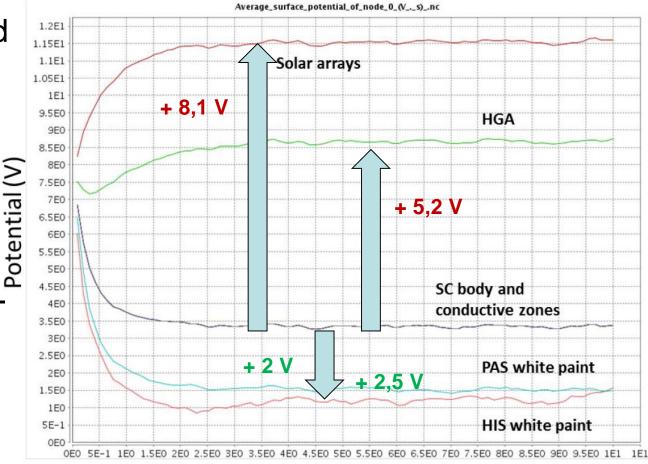

**Reference Test Case at 0.28UA/20eV:** cnes computed without painting If Painting was totally conductive

Conductive parts Potential: + 1,5 V

HGA Potential : +8.0 V

**SUN Face Solar Array:** +15 V

otential (V) This 2<sup>nd</sup> simulation also shows the voltage on all the parts and next simulation (with finite PCBE conductivity) will show the influence of this painting in the 0,28UA case

Time (s)

# Voltage Map at 0,28UA/20eV

This case is more positive than the 1UA one The plasma density is higher, Debye Length is shorter. Thus the voltage extend less far and voltage perturbation around the spacecraft is lower than in the 1UA case

### **COES** Real Test Case at 1UA/8eV: Parametric study of the PCBE conductivity

#### 3 cases under study

- Case 2 : σ = 10-11 Ω-1.m-1

- Case 3 : σ = 10-13 Ω-1.m-1

- Case 4 : σ = 10-15 Ω-1.m-1

In these cases, only painted area have a different voltage compared to the « ideal » case which means that the painted areas have no influence on the global voltage of the S/C. (If a large part of the spacecraft would have been painted it would not be the case anymore)

### CORS Real Test Case at 1UA/8eV : Case 2 : $\sigma$ = 10-11 Ω-1.m-1

PCBE

Steady state is reached fast. It means that the conductivity play its role, and conducted current is equal to the collected one. On PAS and HIS voltage reach a -2V to -2,5V more negative than the structure, which is rather low.

SOLO EMC WG- 8-9 Nov 2016

Time (s)

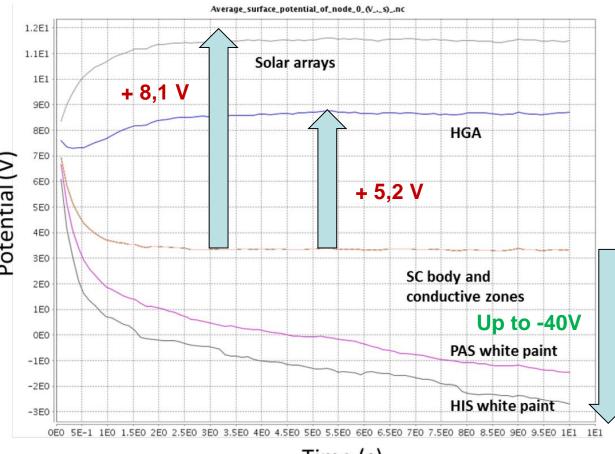

### **COPS** Real Test Case at 1UA/8eV : Case 3 or 4 Others High Resistive painting case

Steady state is not reached fast. It means that the conductivity, too low can't play its role anymore, voltage on the painting decrease: limit estimated to 5Te = -40Volts

NB : This is not the conductivity estimated for the PCBE. We are in the case of another high resistive painting

SOLO EMC WG- 8-9 Nov 2016

Time (s)

### CORES Real Test Case at 0,28UA/20eV : Case 3 or 4 Resistive case

PRE

Conductivity has no more any influence on the voltage of the painting, everything is made with secondary emission which prevent from negative charging Results are compliant with the 1V specification even in the high resistive painting case

PCBE

# CORS Voltage dominated by SEE (Secondary Electronic Emission) or conductivity

**For**  $\sigma$  **above** 10<sup>-11</sup> $\Omega$ <sup>-1</sup>.m<sup>-1</sup>, the secondary emission does't play any role.

•  $\rightarrow$  Voltage is dominated by conductivity

For σ below 10<sup>-11</sup>Ω<sup>-1</sup>.m<sup>-1</sup> Voltage reached depend both on SEE rate and its maximum. The variability in terms of potential will be aroud -2V to -6V depending on temperature, ageing, … (criteria that modify SEE)

### CONES Conclusion

- Direct charging test on PCBE shows large variability in the results (at volt level) on the different samples, it is difficult to precisely measure its good conductivity

- Charge of the painted area has no influence on the voltage spacecraft (while the surfaces are low wrt total S/C surface)

- In all the case the differential potential on painted surface on PAS and HIS are very low and much lower than other parts.

- The worst case is when 2.Te is under the first point of cross over: 028UA/8eV is in this case

Question : what is the probability of occurrence and how long does this phenomenon last ?

- Maximum voltage reachable is -40Volts (Low energy plasma) but only for high painting resistivity (when σ rather below 10<sup>-11</sup> Ω<sup>-1</sup>.m<sup>-1</sup>, which is not the estimation we made of the PCBE conductivity).

- For conductivity around some 10<sup>-11</sup> Ω<sup>-1</sup>.m<sup>-1</sup>, and depending on the conditions some few negative volts are reachable under -1V (Max around –8V or -10 V)

- Albedo photoemission can compensate the voltage (and the possible mitigation was not estimated or taken into account in this study)

- Find a better solution to estimate the real conductivity of the PCBE. And confirm that the PCBE conductivity is above 10<sup>-11</sup> Ω<sup>-1</sup>.m<sup>-1</sup>, (electrode above the painting is not a solution)

- Evaluation the percentage of time where a critical plasma 1UA/8eV is present?

- Evaluation of the perturbation due to a resistive painting on the S/C potential but also HGA and SA potentials should be taken into account.

# **C**COES Reference Documents

#### Références

- [RD1] https://directory.eoportal.org/web/eoportal/satellitemissions/s/solar-orbiter-mission

- [RD2] SPIS Spacecraft Plasma Interaction System http://dev.spis.org

- [RD3] https://www.ucl.ac.uk/mssl/space-plasma-physics/news/msslplasma-solar-orbiter-news/so-news-Q1-2015/SO\_SC\_STM

- [RD4] Technical Data Package SPIS-SCIENCE ESA/ESTEC contract

- [RD5] Étude et simulations des phénomènes d'interactions satelliteplasma et de leurs impacts sur les mesures de plasmas basses énergies / Stanislas Guillemant ; directeurs de thèse, Philippe Louarn, Vincent Génot et Jean-Charles Mateo-Vélez, 2014